Welcome.

My name is Florian and I am currently a PhD student with the Integrated Systems Laboratory of ETH Zurich. My research interest include the design of very large scale integration circuits with particular focus on application specific integrated circuits and their applications in high performance computing. Please don’t hesitate to get in contact with me!

Chips.

As part of my PhD program I have designed and contributed to the following chips:

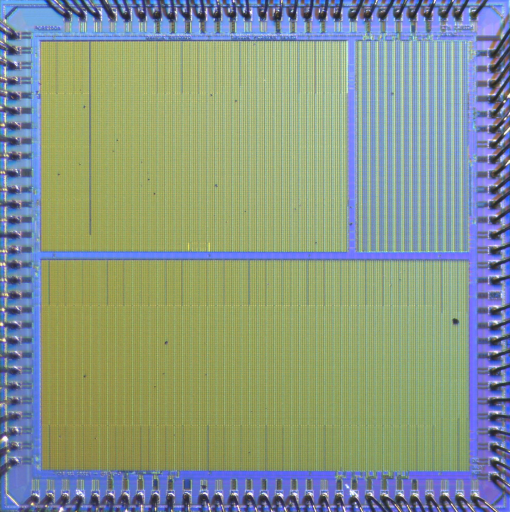

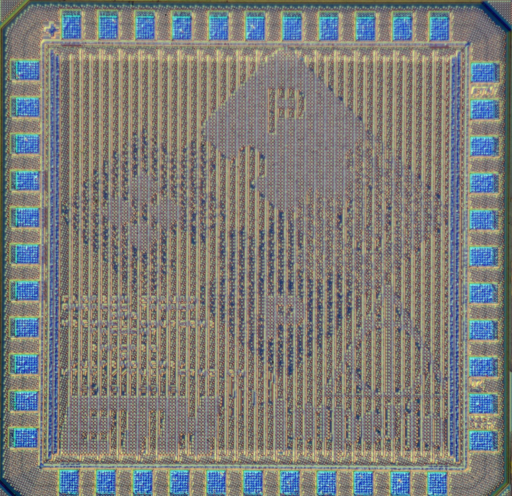

Baikonur (GF22FDX)

Baikonur is the successor of Kosmodrom featuring two Ariane cores and 25 Snitch cores.

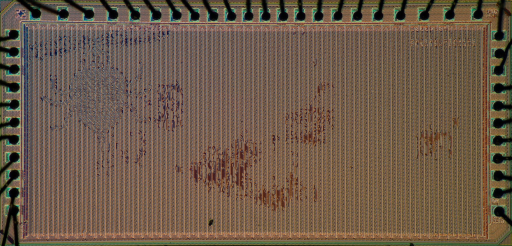

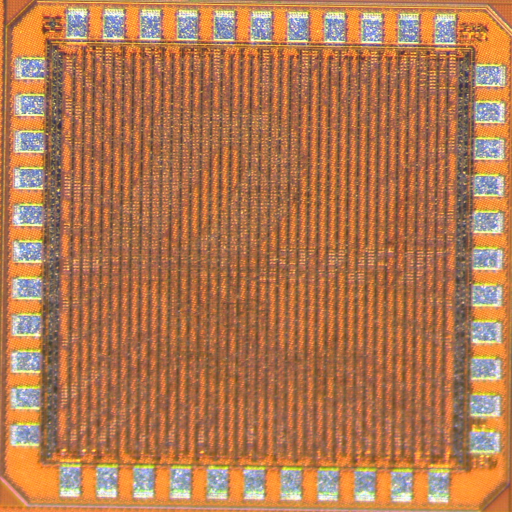

Kosmodrom (GF22FDX)

Kosmodrom features two Ariane cores and a neural network accelerator (NTX).

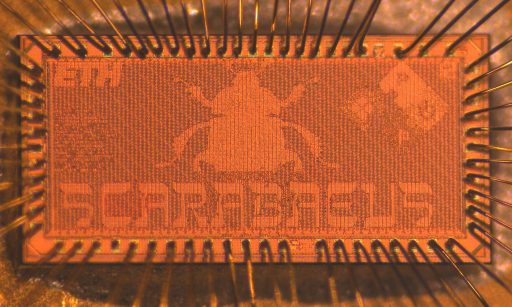

Scarabeus (UMCL65)

Designed by students partially under my supervision. Features one Ariane core and a tensor DMA.

Talks.

(Recorded) Talks:

Publications.

Here is a curated list of publications.

Manticore: A 4096-core RISC-V Chiplet Architecture for Ultra-efficient Floating-point Computing

Florian Zaruba, Fabian Schuiki and Luca Benini

HotChips 2020

FPnew: An Open-Source Multi-Format Floating-Point Unit Architecture for Energy-Proportional Transprecision Computing

Stefan Mach, Fabian Schuiki, Florian Zaruba and Luca Benini

Preprint arXiv (IEEE Transactions on Very Large Scale Integration)

Snitch: A 10 kGE Pseudo Dual-Issue Processor for Area and Energy Efficient Execution of Floating-Point Intensive Workloads

Florian Zaruba, Fabian Schuiki, Torsten Hoefler and Luca Benini

Preprint arXiv (IEEE Transactions on Computers)

Stream Semantic Registers: A Lightweight RISC-V ISA Extension Achieving Full Compute Utilization in Single-Issue Cores

Fabian Schuiki, Florian Zaruba, Torsten Hoefler and Luca Benini

IEEE Transactions on Computers

The Floating Point Trinity: A Multi-modal Approach to Extreme Energy-Efficiency and Performance

Florian Zaruba, Fabian Schuiki, Stefan Mach and Luca Benini

2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS)

Ara: A 1-GHz+ Scalable and Energy-Efficient RISC-V Vector Processor With Multiprecision Floating-Point Support in 22-nm FD-SOI

Matheus Cavalcante, Fabian Schuiki, Florian Zaruba, Michael Schaffner and Luca Benini

IEEE Transactions on Very Large Scale Integration (VLSI) Systems

The Cost of Application-class Processing: Energy and Performance Analysis of a Linux-ready 1.7-GHz 64-bit RISC-V Core in 22-nm FDSOI Technology

Florian Zaruba and Luca Benini

IEEE Transactions on Very Large Scale Integration (VLSI) Systems 27.11 (2019): 2629-2640

OpenPiton+ Ariane: The First Open-Source, SMP Linux-booting RISC-V System Scaling From One to Many Cores

Jonathan Balkind, Katie Lim, Fei Gao, Jinzheng Tu, David Wentzlaff, Michael Schaffner, Florian Zaruba and Luca Benini

Third Workshop on Computer Architecture Research with RISC-V, CARRV

BYOC: A “bring your own core” framework for heterogeneous-ISA research

Jonathan Balkind, Katie Lim, Michael Schaffner, Fei Gao, Grigory Chirkov, Ang Li, Alexey Lavrov, Tri M Nguyen, Yaosheng Fu, Florian Zaruba, Kunal Gulati, Luca Benini and David Wentzlaff

Proceedings of the Twenty-Fifth International Conference on Architectural Support for Programming Languages and Operating Systems